Hello and welcome to exampundit. Here is a set of IBPS SO IT Officer Professional Knowledge Quiz on Computer Architecture for IBPS IT Officer Mains exam 2018.

- Register renaming is done in pipelined processors

(a) as an alternative to register allocation at compile time

(b) for efficient access to function parameters and local variables

(c) to handle certain kinds of hazards

(d) as part of address translation

(e) None of these

- The amount of ROM needed to implement a 4 bit multiplier is

(a) 64 bit

(b) 128 bit

(c) 1 kbit

(d) 2 kbit

(e) None of these

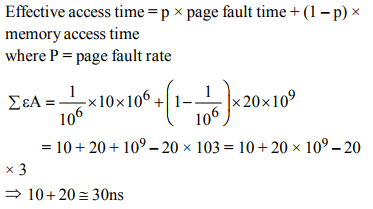

- Let the page fault service time be 10 Ms in a computer with average memory access time being 20 ns. If one page fault is generated for every 106 memory accesses, what is the effective access time for the memory?

(a) 21 ns

(b) 30 ns

(c) 23 ns

(d) 35 ns

(e) None of these

- A computer handles several interrupt sources of which of the following are relevant for this question.

Interrupt from CPU temperature sensor (raises interrupt if CPU temperature is too high)

Interrupt from Mouse (raises Interrupt if the mouse is moved or a button is pressed)

Interrupt from Keyboard (raises Interrupt if a key is pressed or released)

Interrupt from Hard Disk (raises Interrupt when a disk read is completed)

Which one of these will be handled at the HIGHEST priority?

(a) Interrupt from Hard Disk

(b) Interrupt from Mouse

(c) Interrupt from Keyboard

(d) Interrupt from CPU temperature sensor

(e) None of these

- How many 32 k × 1 RAM chips are needed to provide a memory capacity of 256 kbyte?

(a) 8

(b) 32

(c) 64

(d) 128

(e) None of these

- A CPU generally handles an interrupt by executing an interrupt service routine

(a) as soon as an interrupt as raised

(b) by checking the interrupt register at the end of fetch cycle

(c) by checking the interrupt register after finishing the execution of the current instruction

(d) by checking the interrupt register at fixed time intervals.

(e) None of these

- For a magnetic disk with concentric circular tracks, the seek latency is not linearly proportional to the seek distance due to

(a) non-uniform distribution of requests

(b) arm starting and stopping inertia

(c) higher capacity of tracks on the periphery of the platter

(d) use of unfair arm scheduling policies

(e) None of these

- Consider a 4-way set associate cache consisting of 128 lines with a line size of 64 words. The CPU generates a 20-bit address of word in main memory. The number of bits in the TAG, LINE and WORD fields are respectively.

(a) 9, 6, 5

(b) 7, 7, 6

(c) 7, 5, 8

(d) 9, 5, 6

(e) None of these

- Consider a disk pack with 16 surfaces, 128 tracks per surface and 256 sectors per track. 512 byte of data are stored in a bit serial manner in a second. The capacity of the disk pack and the number of bits required to specify a particular section in the disk are respectively

(a) 256 Mbyte, 19 bit

(b) 256 Mbyte, 28 bit

(c) 512 Mbyte, 20 bit

(b) 64 Gbyte, 28 bit

(e) None of these

- A CPU has 24-bit instructions. A program starts at address 300 (in decimal). Which one of the following is a legal program counter (all values in decimal)?

(a) 400

(b) 500

(c) 600

(d) 700

(e) None of these

Regards

Team EP